吉林大學計算機系統(tǒng)結構 第三章 指令級并行學習筆記(曲冠南老師版)

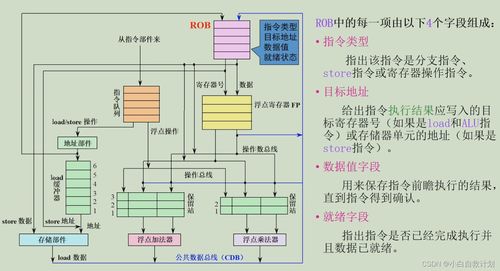

指令級并行(Instruction-Level Parallelism, ILP)是計算機系統(tǒng)結構中的核心概念,旨在通過指令流水線、多發(fā)射和動態(tài)調(diào)度等技術提高程序執(zhí)行效率。本章基于曲冠南老師的講解,結合計算機系統(tǒng)集成與開發(fā)的實際應用,總結了指令級并行的基本原理、關鍵技術與挑戰(zhàn)。\n\n一、指令級并行的基本概念\n指令級并行指處理器在單個程序內(nèi)同時執(zhí)行多條指令的能力。它依賴于硬件和編譯器的協(xié)同優(yōu)化,以挖掘指令間的獨立性。在計算機系統(tǒng)集成中,ILP是實現(xiàn)高性能計算的關鍵,尤其在開發(fā)復雜軟件系統(tǒng)時,能夠顯著提升吞吐量。\n\n二、關鍵技術\n1. 流水線技術:將指令執(zhí)行劃分為多個階段(如取指、譯碼、執(zhí)行、訪存、寫回),允許不同指令在不同階段重疊執(zhí)行。曲冠南老師強調(diào),流水線深度需平衡性能與硬件復雜度,避免結構沖突、數(shù)據(jù)沖突和控制沖突。\n\n2. 多發(fā)射與超標量架構:處理器每個時鐘周期發(fā)射多條指令,通過硬件動態(tài)調(diào)度(如Tomasulo算法)或靜態(tài)編譯優(yōu)化(如VLIW)實現(xiàn)并行。在系統(tǒng)開發(fā)中,這要求編譯器進行指令調(diào)度,以最大化資源利用率。\n\n3. 動態(tài)分支預測:通過歷史記錄預測分支指令結果,減少流水線停頓。曲冠南老師指出,現(xiàn)代處理器使用混合預測器,結合局部和全局歷史,在集成系統(tǒng)中提高預測準確率。\n\n4. 循環(huán)展開與軟件流水:編譯器技術,通過展開循環(huán)體增加指令并行度,減少依賴。在開發(fā)高性能應用時,這些方法可優(yōu)化關鍵代碼段。\n\n三、挑戰(zhàn)與局限性\nILP受限于指令間依賴(如數(shù)據(jù)依賴、控制依賴)和硬件資源。真實程序中固有并行度有限,過度優(yōu)化可能導致功耗增加和設計復雜化。曲冠南老師提醒,在系統(tǒng)集成中需權衡ILP收益與成本,避免Amdahl定律的瓶頸。\n\n四、與系統(tǒng)集成和開發(fā)的關聯(lián)\n在計算機系統(tǒng)集成中,ILP技術直接影響CPU選型和架構設計。開發(fā)者需理解ILP原理,以編寫優(yōu)化代碼或配置編譯器。例如,在嵌入式系統(tǒng)開發(fā)中,利用ILP可提升實時性能;而在服務器集成中,超標量處理器支持高并發(fā)任務。\冠南老師的教學強調(diào)理論與實踐結合,鼓勵學生通過模擬器(如SimpleScalar)實驗ILP效果,為未來從事系統(tǒng)開發(fā)奠定基礎。\n\n指令級并行是提升計算機系統(tǒng)性能的重要手段,通過硬件與軟件協(xié)同,在系統(tǒng)集成和開發(fā)中發(fā)揮關鍵作用。掌握其原理有助于設計高效、可擴展的計算平臺。

如若轉(zhuǎn)載,請注明出處:http://www.bpxtzif.cn/product/22.html

更新時間:2026-04-12 19:12:03